기술이전 상세 정보를 불러오는 중입니다...

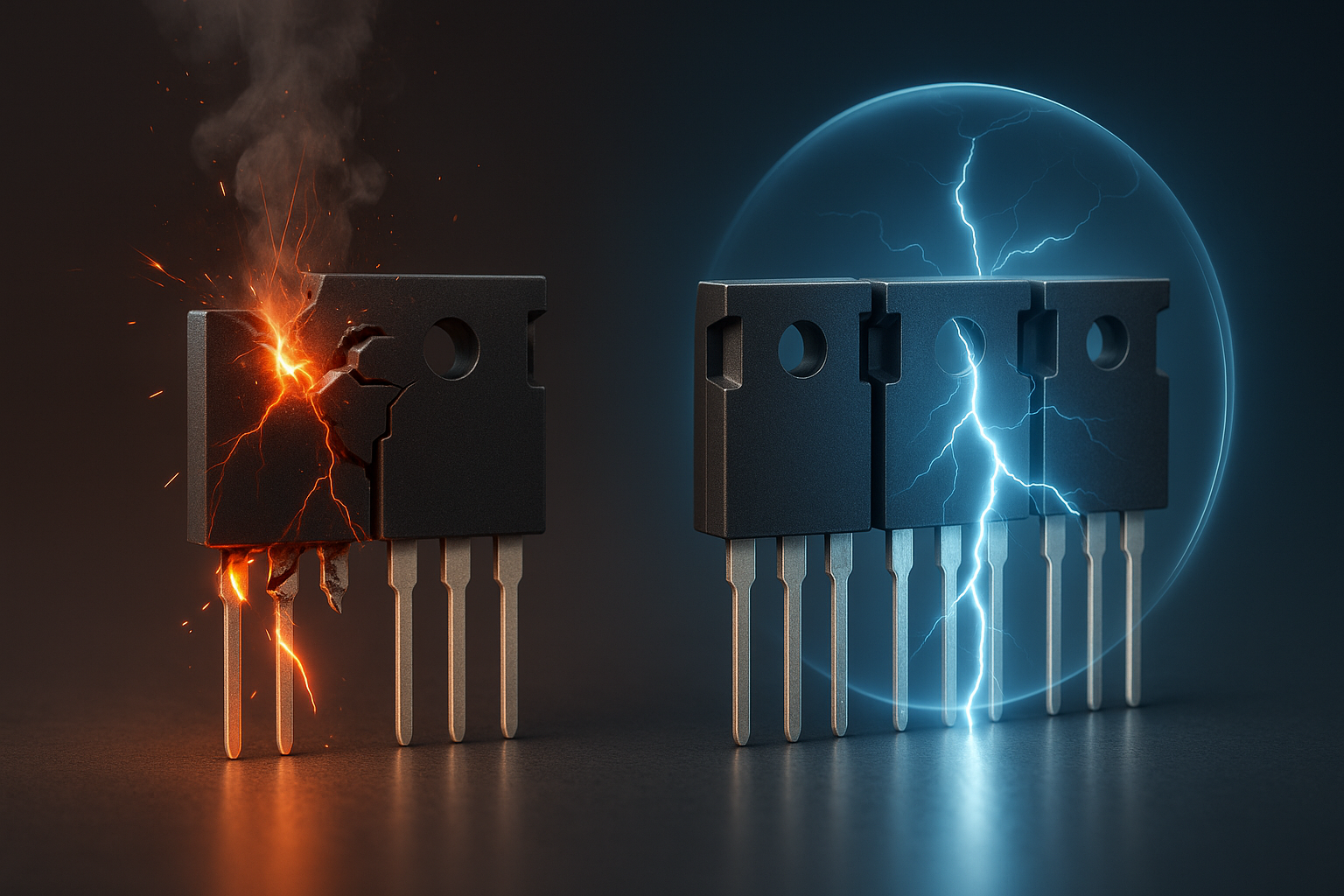

[기술 요약] 초고전압 스위칭 시 직렬 연결 트랜지스터의 스위칭 시간 불균일로 인한 파괴 및 펄스 상승 시간 지연은 심각한 문제입니다. 본 기술은 복수개의 전계 효과 트랜지스터를 병렬 연결한 과전압 방지부를 통해 각 트랜지스터에 인가되는 전압을 균등하게 분배하고 제한합니다. 이 과전압 방지부는 FET의 다이오드 특성을 활용하여 제너 다이오드처럼 작동하며, 나노초(ns) 단위의 고속 응답으로 과전압을 즉시 억제합니다. 이로써 트랜지스터 파괴를 방지하고, 급격한 드레인 소스 전압 증가 및 펄스 상승 시간 지연 문제를 해결하여, 고전압 스위칭 회로의 안정성과 신뢰성을 획기적으로 향상시키고 제품 성능을 극대화합니다.

초고전압 스위칭 시 직렬 연결 트랜지스터의 스위칭 시간 불균일로 인한 파괴 및 펄스 상승 시간 지연은 심각한 문제입니다. 본 기술은 복수개의 전계 효과 트랜지스터를 병렬 연결한 과전압 방지부를 통해 각 트랜지스터에 인가되는 전압을 균등하게 분배하고 제한합니다. 이 과전압 방지부는 FET의 다이오드 특성을 활용하여 제너 다이오드처럼 작동하며, 나노초(ns) 단위의 고속 응답으로 과전압을 즉시 억제합니다. 이로써 트랜지스터 파괴를 방지하고, 급격한 드레인 소스 전압 증가 및 펄스 상승 시간 지연 문제를 해결하여, 고전압 스위칭 회로의 안정성과 신뢰성을 획기적으로 향상시키고 제품 성능을 극대화합니다.

| 기술 분야 | 전력 반도체 과전압 보호 회로 |

| 판매 유형 | 자체 판매 |

| 판매 상태 | 판매 중 |

| 기술명 | |

| 복수개의 직렬 연결 방식 트랜지스터 스위치의 과전압 방지 회로 | |

| 기관명 | |

| 기초과학연구원 | |

| 대표 연구자 | 공동연구자 |

| 정인일 | - |

| 출원번호 | 등록번호 |

| 1020160123397 | 1020076800000 |

| 권리구분 | 출원일 |

| 특허 | 2016.09.26 |

| 중요 키워드 | |

나노초 동작과전압 방지 회로고전압 스위칭회로 안정성스위칭 신뢰성반도체 스위치 | |

기술이전 상담신청

연구자 미팅

기술이전 유형결정

계약서 작성 및 검토

계약 및 기술료 입금

보유 기술 로딩 중...

인기 게시물 로딩 중...