기술이전 상세 정보를 불러오는 중입니다...

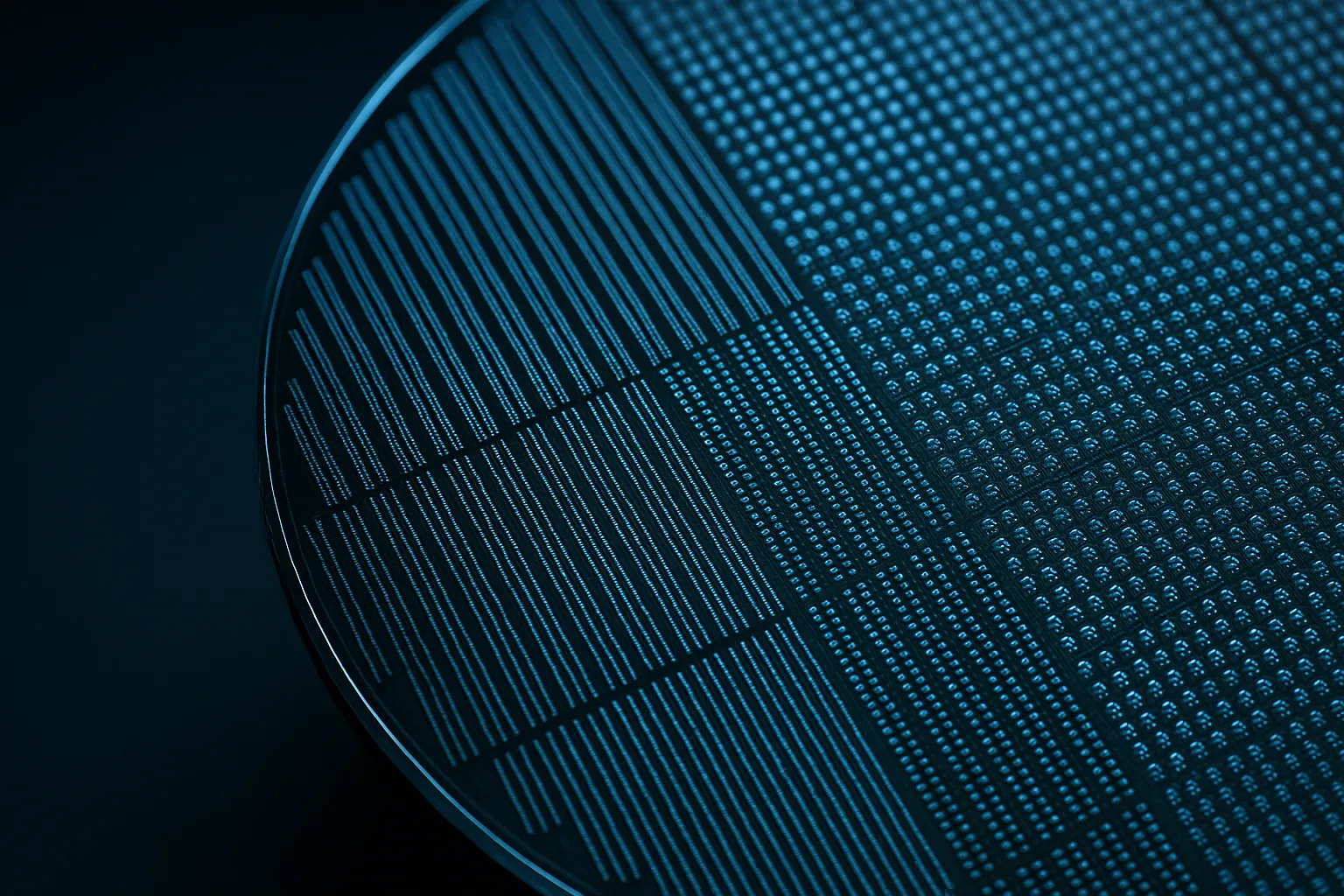

[기술 요약] 기존 반도체 미세 공정은 30nm 이하 구현에 한계가 있었으며, 블록공중합체 기반 패터닝 기술 또한 10nm 이하 구조에서 낮은 세그먼트 상호작용으로 어려움을 겪었습니다. 본 기술은 이러한 문제를 해결하기 위해 블록공중합체의 자기조립 특성을 활용합니다. 유기물 포토레지스트와 블록공중합체 박막을 형성한 후 선택적으로 단위체 블록을 제거하고 무기 스페이서층을 증착하여 고밀도 나노 패턴을 형성합니다. 이를 통해 기존 대비 2배 높은 패턴 밀도를 구현하며, 5nm 이하의 정밀한 피치 및 주기 조절이 가능합니다. 이 나노 패턴은 높은 에칭 저항성을 지녀 마스크로 활용, 하부 기판에 5nm 이하의 미세 패턴을 손쉽게 전송할 수 있습니다. 결과적으로 반도체 및 전자기기 회로의 고집적화를 달성하여 메모리 밀도, 신뢰성, 저전력 소비 향상에 기여할 수 있습니다.

기존 반도체 미세 공정은 30nm 이하 구현에 한계가 있었으며, 블록공중합체 기반 패터닝 기술 또한 10nm 이하 구조에서 낮은 세그먼트 상호작용으로 어려움을 겪었습니다. 본 기술은 이러한 문제를 해결하기 위해 블록공중합체의 자기조립 특성을 활용합니다. 유기물 포토레지스트와 블록공중합체 박막을 형성한 후 선택적으로 단위체 블록을 제거하고 무기 스페이서층을 증착하여 고밀도 나노 패턴을 형성합니다. 이를 통해 기존 대비 2배 높은 패턴 밀도를 구현하며, 5nm 이하의 정밀한 피치 및 주기 조절이 가능합니다. 이 나노 패턴은 높은 에칭 저항성을 지녀 마스크로 활용, 하부 기판에 5nm 이하의 미세 패턴을 손쉽게 전송할 수 있습니다. 결과적으로 반도체 및 전자기기 회로의 고집적화를 달성하여 메모리 밀도, 신뢰성, 저전력 소비 향상에 기여할 수 있습니다.

| 기술 분야 | 반도체 미세패터닝 |

| 판매 유형 |

| 자체 판매 |

| 판매 상태 | 판매 중 |

기술이전 상담신청

연구자 미팅

기술이전 유형결정

계약서 작성 및 검토

계약 및 기술료 입금

보유 기술 로딩 중...

인기 게시물 로딩 중...